Design

LFSR is used in various algorithms to generate a deterministic stream of numbers.

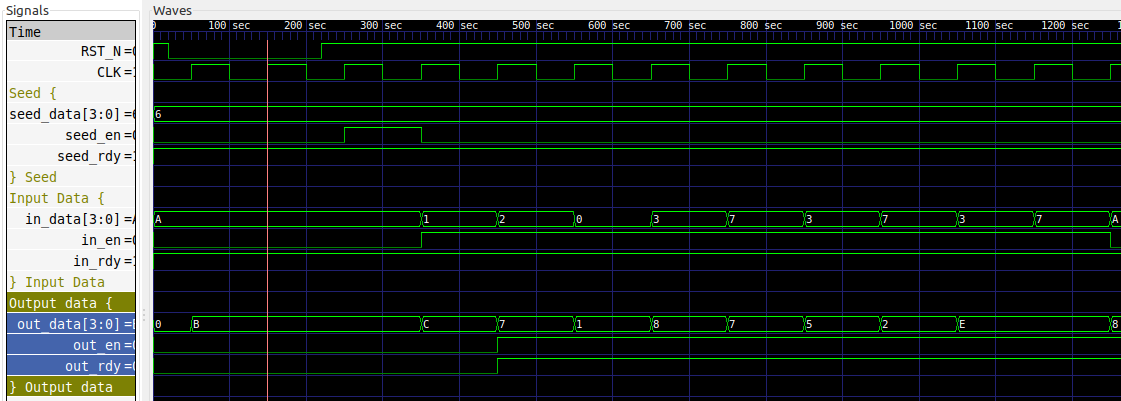

This design implements a 4 bit scrambler where the 4 bit LSFR implements the equation $ X^3 + 1 $

Operation of the design is as follows.

- At start a seed value is loaded in the LFSR.

- For every valid input data.

- The current value of the LFSR is xored with the input data

- The xored value is sent out.

- Next value of LFSR is generated.

- If there is no valid input no output is generated.

- If the output is not consumed by the sink, the design does not accept any new input.

Bus Protocol.

Data is transferred from Source to Sink when the following conditions are met.

- Source has Data to send(Signal *_en is high)

- Sink is Ready to accept data. (Signal *_rdy is high)

Every bus interface has atleast 3 signals rdy,en and data. A transaction is said to have occured during the cycle where en and rdy are high.

Note Verilog Implementation is available at scrambler.v You can use this to verify your test environment.