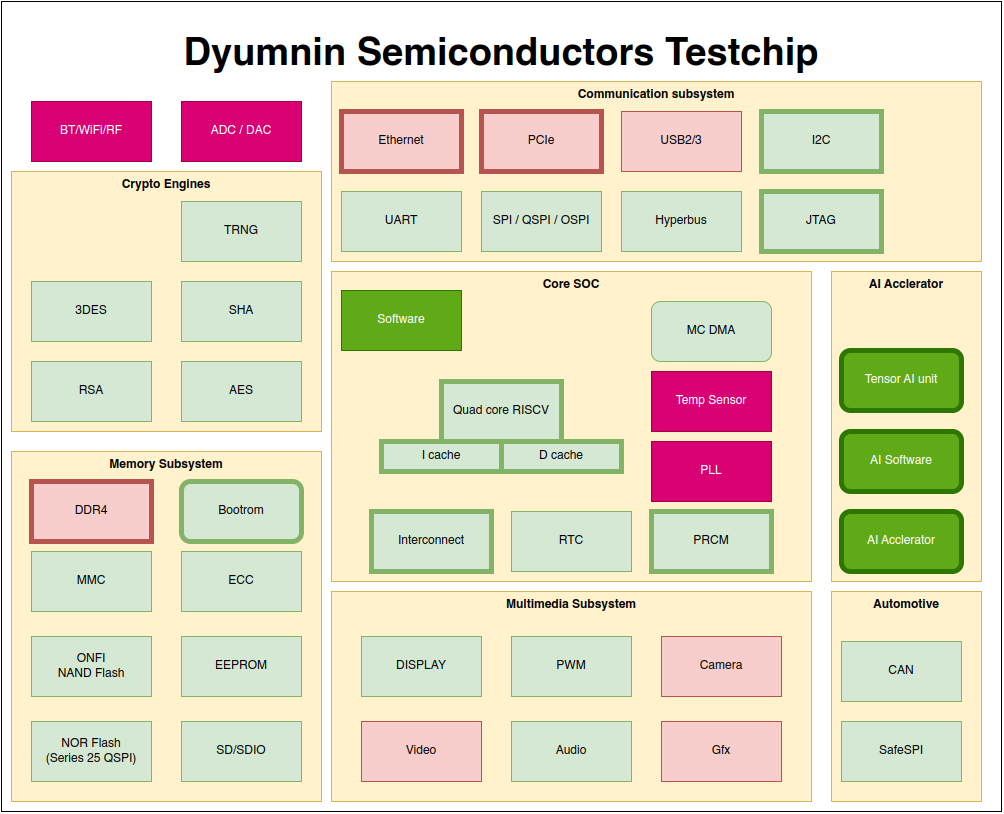

RISCV SOC

We are working on a RISCV Soc design whose peripheral list has "everything including the kitchen sink". The goal is to have a proven reference design and the ecosystem around it and enable our clients to build their chip on a proven platform and achive rapid time to market.

RISCV SOC

Dyumnin’s RISCV SOC is built around a 64bit Quad core server class RISCV CPU. The chip has one or more of the following subsystems.

- AI/ML subsystem

- Automotive subsystem

- Multimedia Subsystem

- Memory subsystem

- Cryptographic subsystem

- Communication subsystem.

The testchip will be available as an FPGA for evaluation and testing.

Each subsystem has one or more of the associated IP’s. And based on the enduser requirement a new SOC can be spun with the custom peripherals required by the enduser application.

Core SoC

The core SOC consists of a Quad code server class RISCV CPU with the other components required for a functional CPU subsystem. In future it will be possible to replace this subsystem with a custom core.

AI Acclerators.

The AI accelerator system consists of a custom CPU tightly coupled with a tensor flow unit for accelerating common AI operations.

Multimedia Subsystem

The multimedia subsystem contains IP for

- HDMI,

- Display Port,

- MIPI,

- Camera Subsystem,

- Gfx accelerators and

- Digital Audio.

Memory Subsystem

This consists of the IP’s required to connect to most of the memory chips and modules available in the market. This includes

- DDR,

- MMC,

- ONFI,

- NorFlash,

- SD/SDIO protocols.

Communication subsystem

The communication subsystem supports most of the protocols used to connect between devices e.g.

- PCIe,

- Ethernet,

- USB,

- SPI,

- I2C,

- UART etc.

Automotive subsystem

CAN, CAN-FD and SafeSPI IP’s are available to connect to automotive systems.